## **CMP Technological Paradigm Shift To Surface Cleaning**

**Hong Jin Kim**

Advanced Module Engineering, GLOBALFOUNDRIES

#### **Presentation Focus On...**

#### CMP-induced Defects:

- -. CMP Process

- -. Role and Effect of CMP in-situ Cleaning

- -. Brush Cleaning

- -. Examples of CMP-induced Defects and Their Removal

Cleaning Perspective of CMP Process

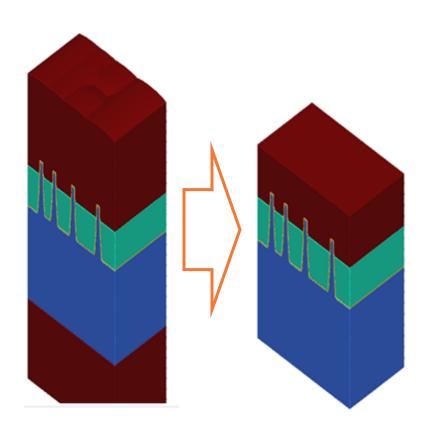

#### **CMP: Planarization Technology**

**Planarization & Polishing**

**Material Removal & Separation**

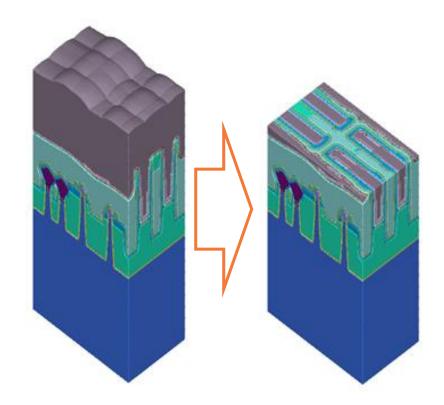

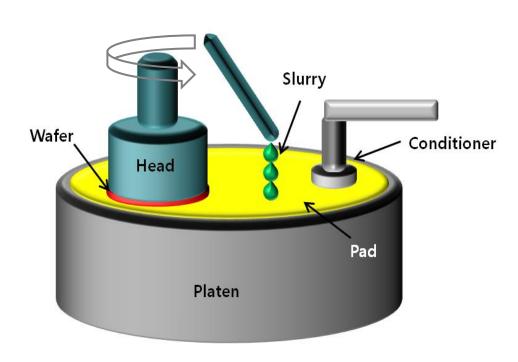

#### **CMP Equipment: Polisher and Cleaner**

#### **Polisher**

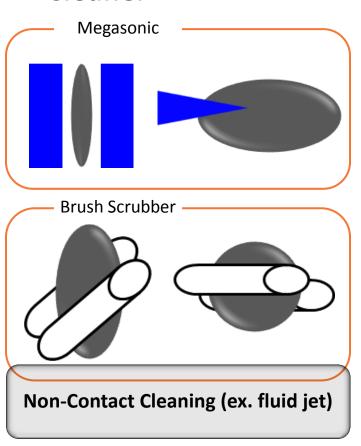

#### Cleaner

Polishing and cleaning are in-situ process: polishing  $\rightarrow$  cleaning at the same equipment

#### **Historical CMP Technology Development**

1927, Preston published glass polishing theory

1972, Raytheon, first practice CMP for planarization

1983, IBM first planarized Pbsilicate glass for STI

1983, IBM first planarized Pbsilicate glass for STI

1986, CMP developed in IBM, called FRED

1987, CMP development begin at IBM

1989, oxide/AI/W CMP implemented 1991, IC pad born 1995, 1st ph.D for CMP 1997, 1st CMP textbook

2000, 300mm CMP setup in industry for manufacturing

2000 - 2010, CMP developed explosively in materials, consumables, tools and functions

2017, Core process in the semiconductor manufacturing

Michael Fury, "You want to do what to my wafer", Korea CMP User Group Meeting 2014 Gautam Banerjee and Robert L. Rhoades, "Chemical Mechanical Planarization: Historical Review and Future Trend", ECS Transactions, 2008 Images from google

#### **ITRS Roadmap**

#### **Transistor Scaling:**

- 1. Geometrical Scaling (~ 2003)

- 2. Equivalent Scaling (~ 2021)

- 3. Power Scaling ( $\sim 203x$ )

P. Gargini, SPCC2016

Practical scaling may end at 10nm? Or 7nm will be an end of scaling?

http://spectrum.ieee.org/semiconductors/devices/transistors-could-stop-shrinking-in-2021

#### **Post CMP in-situ Cleaning**

CMP: is known as the most defect generated process in semiconductor fabrication However, <u>CMP is also highly favorable process condition for cleaning aspect</u>

cf. Challenges of wet cleaning (ex-situe): pattern damage, strong adhesion of small particle (at dry surface state) to wafer surface

#### CMP (pros and cons as cleaning perspectives):

- In-situ process

- Flat surface: no pattern damage → strong physical cleaning acceptable

- Single wafer process

- Wet process: weak adhesion between particle and wafer surface

- Sufficient material undercut

- No standard method to estimate particle removal efficiency

- Variation in incoming wafer surface and defect level is very high

- Limited cleaning chemical available for manufacturing (HF, SC-1, NH4OH...)

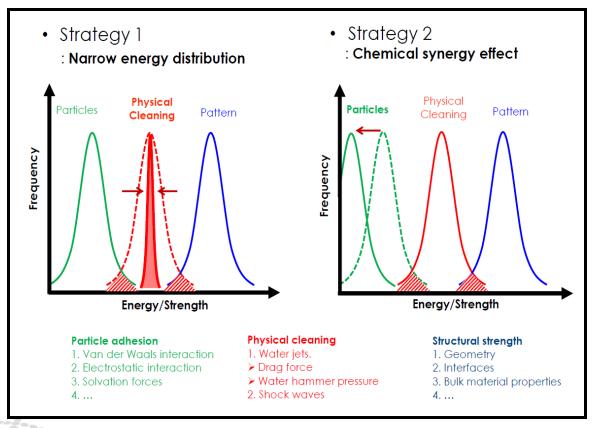

#### **Strategy for Post CMP In-situ Cleaning**

#### Wet Cleaning Strategy for the Next Generation

- Cleaner

- Clean chemical

- Dryer

- Brush, Brush

- •

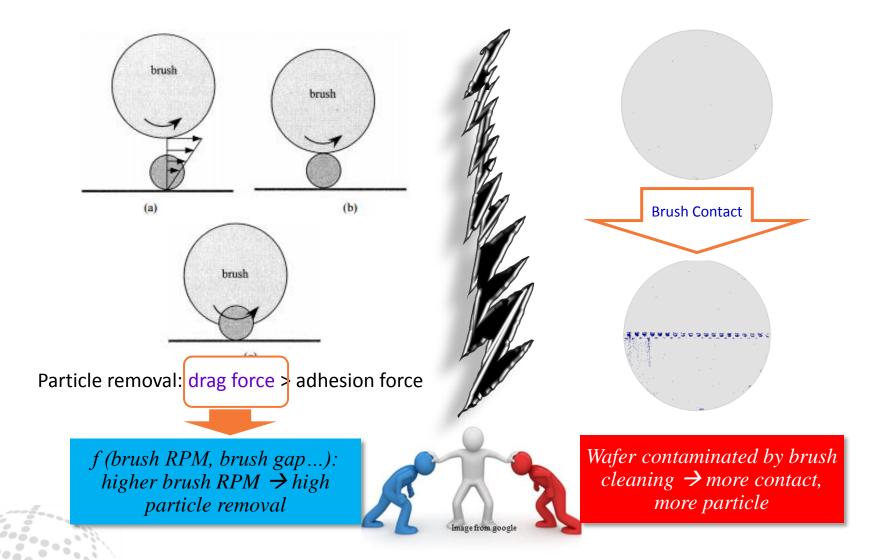

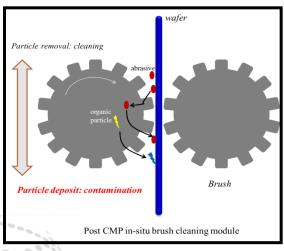

#### **Particle Removal vs Contamination**

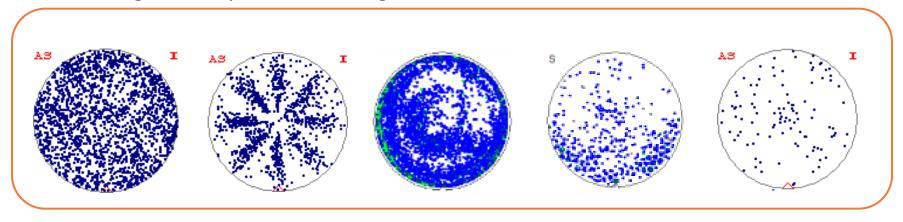

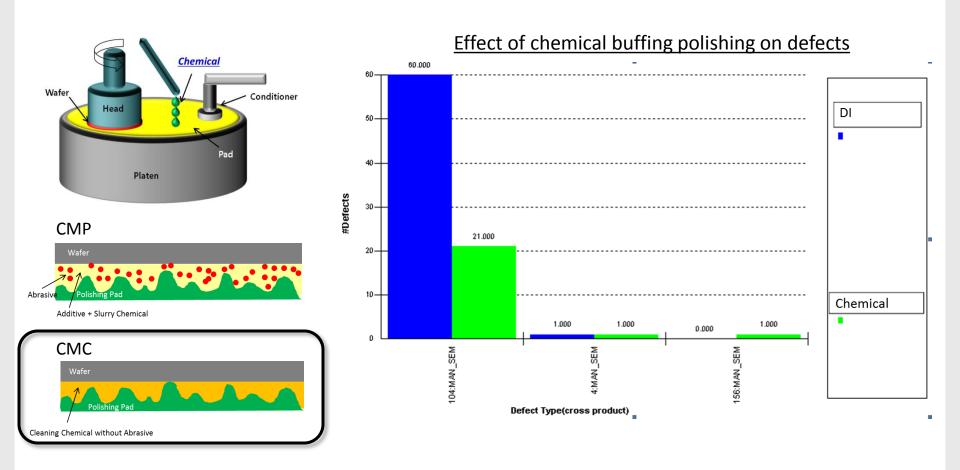

#### **Brush Cleaning and Defect Signature**

Defect Signature by Brush Cleaning

Brush Cleaning is NOT ONLY clean the wafer BUT ALSO contaminate wafer  $\rightarrow$  PRE vs C.C.

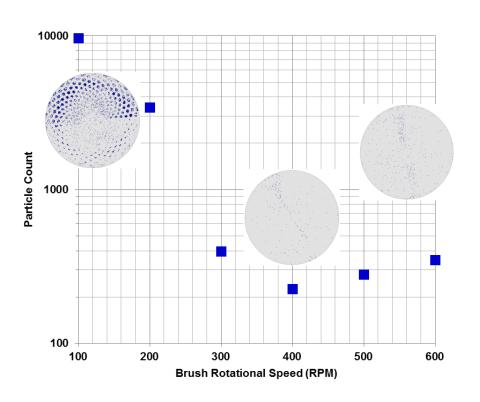

#### **Effect of Brush Recipe on Cross Contamination**

Low RPM → longer contact duration → high cross contamination

Optimum RPM →

high PRE &

optimum

duration →

lowest cross

contamination

High RPM → high contact frequency → increase cross contamination

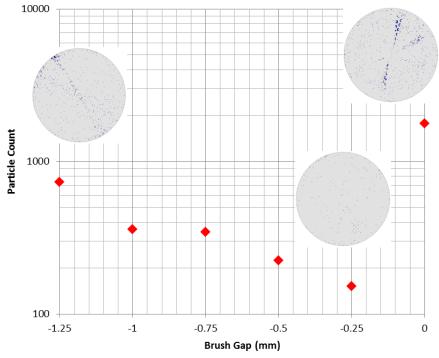

<u>Negative brush gap</u>  $\rightarrow$  high down force  $\rightarrow$  increase contact area  $\rightarrow$  high cross contamination

<u>At 0 gap</u> → nodule non-uniformity → high cross contamination/ low PRE

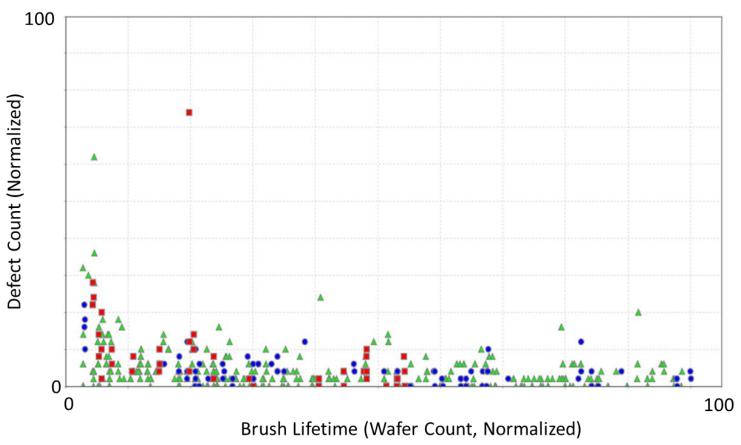

#### **Effect of Brush Lifetime**

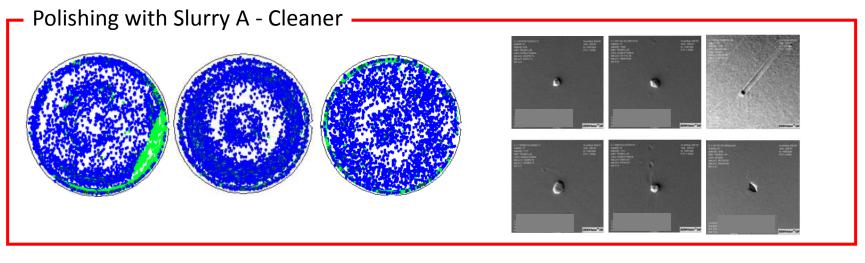

#### **Effect of Slurry – Incoming Wafer Effect**

CMP cleaner performance is sensitively influenced by slurry

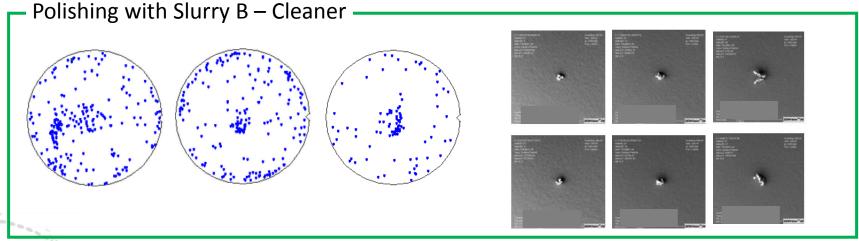

#### **Effect of Cleaner Contamination**

1<sup>st</sup> cleaner loaded defects more than following cleaner. Contamination depends on tool.

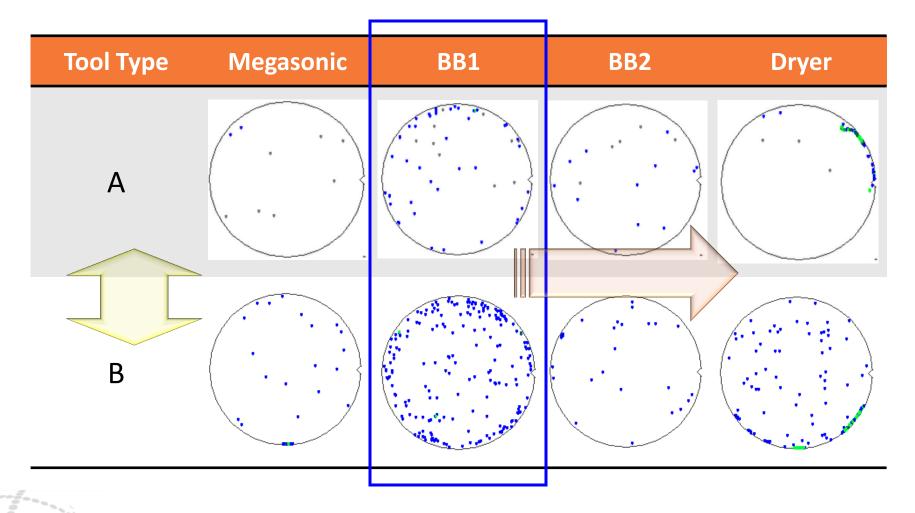

#### **Chemical Mechanical Cleaning**

Buff CMP with cleaning chemical: "Chemical Reaction + Physical Force" to "Wet Wafer Surface" → Effective CLEANING process. No (Min.) material removal required (not matured process in industry yet)

#### **Challenges and Opportunities**

## Brush Cleaning

- Early brush defect

- Minimize cross contamination

- New design of brush and brush nodule

- Pre-broken brush

- Optimized brush properties, ex) porosity, pore size, softness

#### Clean Chemical

- Almost same chemicals used for more than 15 years

- High performance of particle removal associated with brush cleaning

- No material damage with multi materials exposure

- Low cost, eco-friendly chemical (in particular, for Cu CMP)

### **Cleaner Module**

- Non-contact type cleaner module

- New design on cleaner module for advanced cleaning

- Monitoring for dryer

#### **Summary**

Paradigm need to be shifted....

# Planarization / Polishing

CMP concept now encompasses "cleaning" in addition to traditional planarization concept. And role of cleaning becomes much more critical than previous device.

CMP → CMPC: Chemical Mechanical Polishing and Cleaning