Post CMP Cleaning Conference @ SPCC2017

## Post CMP Surface Preparation in sub 10 nm Devices

March 27, 2017 Jin-Goo Park

Department of Materials Engineering, Hanyang University ERICA, Ansan, 15588, KOREA

Nano-Bio Electronic Materials and Processing Lab.

#### 01 Challenges in surface preparation

- Research trend in cleaning technology

- Lesson learned from current cleaning technology

#### <sup>02</sup> Challenges in post CMP surface preparation

- New paradigm in CMP process

- Current post CMP cleaning process

- New direction

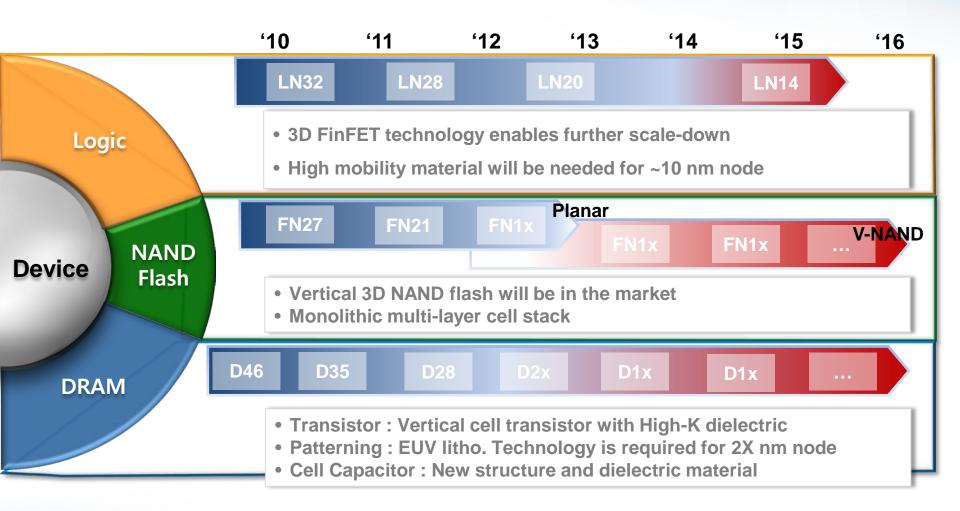

## **Device Technology Roadmap**

## **Device Technology Roadmap**

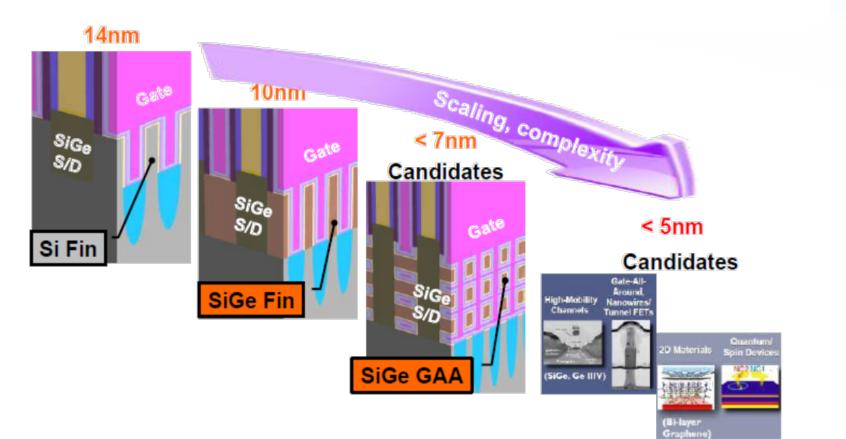

- Scaling and structures are more complex

- Damage-free particle removal much more important

Screen, MRS 2016

Courtesy of imec

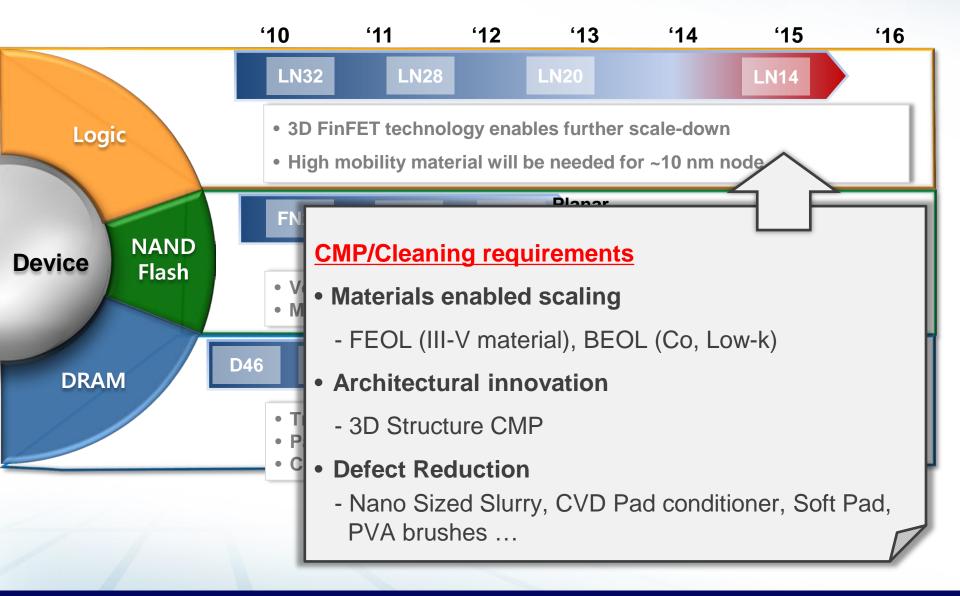

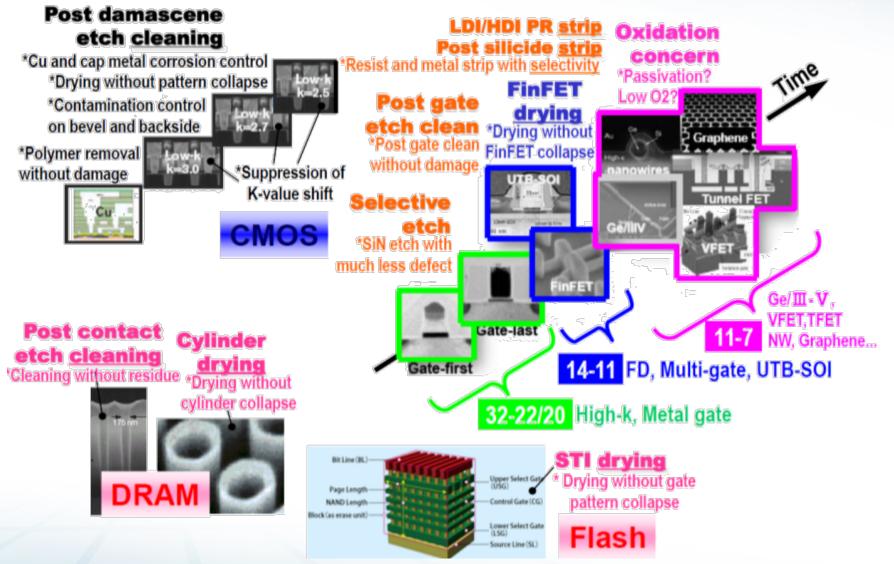

## **Devices Cleaning Challenges**

J. Snow, "Advanced Particle Removal Techniques for ≤20nm Device Node", SPCC (2012)

Nano-Bio Electronic Materials and Processing Lab.

#### Issues

- Nanometer Feature Size

- New Materials

- Nanometer Thin Film

- Single Wafer Cleaning

- CMP Process

- EUVL Process

- 3D Device

- High Aspect Ratio

#### Challenges

- Clean without Etching

- Non RCA (H<sub>2</sub>O<sub>2</sub> based) Chemistry

- Clean without Pattern Damage

- No Megasonics and Brushes

- CMP Induced Defects

- (nano particles and organic defects)

- Zero Defect on EUVL Mask/Pellicle

- Drying without pattern leaning

- High selectivity dry etching/cleaning

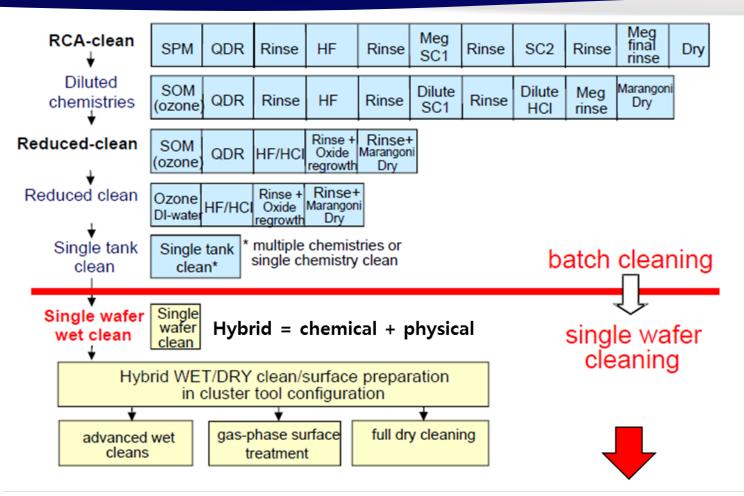

## Cleaning sequences: roadmap

#### No Material loss and Damage Free Cleaning???

Rita Vos and Paul Mertens, "General aspects of cleaning Sequences", UCPSS (2010)

#### **Traditional Wafer Cleaning Chemicals and Technology**

- SC-1(NH<sub>4</sub>OH+H<sub>2</sub>O<sub>2</sub>+H<sub>2</sub>O=1:1:5 at 80 ~ 90°C)

Particles and organic contamination removal

- SC-2(HCI+H<sub>2</sub>O<sub>2</sub>+H<sub>2</sub>O=1:1:5) at 80 ~ 90 °C )

Trace and Noble Metal removal

- Piranha(H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>=4:1 at 9

Organic Contamination ren

- HF (+ H<sub>2</sub>O<sub>2</sub>) : Last wet cleani - HF : Native oxide and H<sub>2</sub>O<sub>2</sub>

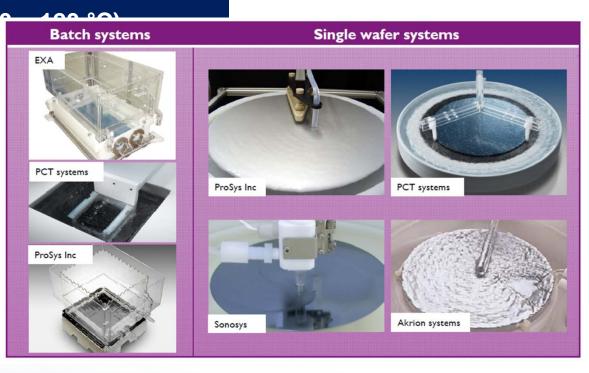

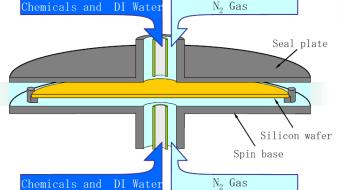

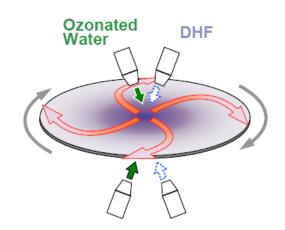

## Single Wafer Cleaning Technology

Single wafer offers significant advantages over batch processes

- Reduces power uniformity problem from a 3dimensional to a 2-dimensional geometry

- + usual single wafer benefits:

- Defect control (cross-contamination, etc.)

- Chemical control & selectivity

- Backside isolation

#### Single Wafer vs. Wet Bench Cleans

All Cleans on Wet Bench  $\Rightarrow$  Overetched Hard Mask

All Single Wafer Cleans  $\Rightarrow$  Reduced overetch  $\Rightarrow$  Improved Selectivity

#### **Cleaning of Fragile Structures**

Damage to poly-gate-stack lines vs. Part. Rem. Eff. 78-nm SiO<sub>2</sub> 1.E+5 (#/wafer) liq. aerosol 1.E+4 tool A all physical cleaning 1.E+3 megasonic ▲ tool F methóds yield **Cleaning defects** tool G higher PRE at 1.E+2 expense of increased damage 1.E+1 1.E+0 [G. Vereecke et al, UCPSS 2006] 20 40 60 80 100 0 PRE (%)

first sight: liquid aerosol gives best performance, but:

- lower performance of megasonic is attributed to non-uniformity,

→ may be overcome by appropriate engineering? other: conc. diss. gas Xc

- behaviour for further scaled features, particles remains to be tested

- cleaning inside vias and trenches needs to be compared

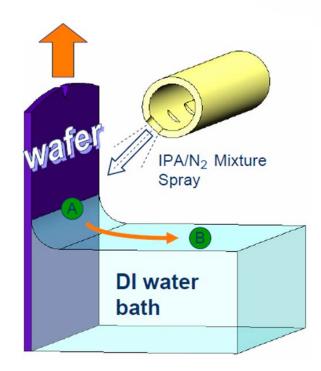

#### Spin dryer –DI water, liquid IPA, vapor IPA, hot IPA

#### A в С Drying IPA vapor (Rotagoni, spin) **IPA Liquid (Spin)** IPA Vapor (spin) Liquid IPA IPA Nozzle PA Vapor nozzle fix of scan IPA Dryer TEL etc Goldfinger NMD Dryer -IPA vapor -Liquid IPA : low surface tension -Rotational force + marangoni force -IPA Nozzle fix or scan to -Controllable of IPA eject wafer edge angle

#### Marangoni IPA dryer

## CMP Challenges in 10 nm/7 nm

| <b>16</b> |         |              |         | TSV Cu      |      |

|-----------|---------|--------------|---------|-------------|------|

| <b>15</b> |         |              |         | 9-10 Cu     |      |

| 14        |         |              | TSV Cu  | W-CA/CB     |      |

| <b>13</b> |         |              | 9-10 Cu | SIOC        |      |

| 12        |         |              | W-CA/CB | TI ILD      |      |

| 11        |         |              | RM      | GP          |      |

| <b>10</b> |         |              | W-TS    | МО          |      |

| 9         |         |              | W-Gate  | SiN Cap     |      |

| 8         |         | TSV Cu       | POC     | W-Gate      |      |

| 7         |         | 9-10 Cu      | ILD2    | ILD2        |      |

| 6         |         | W-CA/CB      | ILD1    | ILD1        |      |

| 5         |         | W-TS         | GP      | TI ILD      |      |

| 4         | 9-10 Cu | Al Gate      | MO      | GP          |      |

| 3         | W       | ILD2         | RB      | MO          | BEOL |

| 2         | Oxide   | ILD1         | STI2    | Nit Buff    | MOL  |

| 1         | STI     | STI          | STI1    | STI         | FEOL |

| •         | 28nm    | <b>20</b> nm | 14nm    | <b>10nm</b> |      |

- <u>Number of CMP steps doubled from 28nm to 10nm node</u> in order to enable new integration schemes such as replacement metal gate and self-aligned contact.

- ~ <u>75% of the increase is in MOL</u> due to the complexity of contact module.

- New CMP processes such as <u>Co, Cap SiN and SiOC</u> CMP in MOL

J. Han, CSTIC, 2016

1

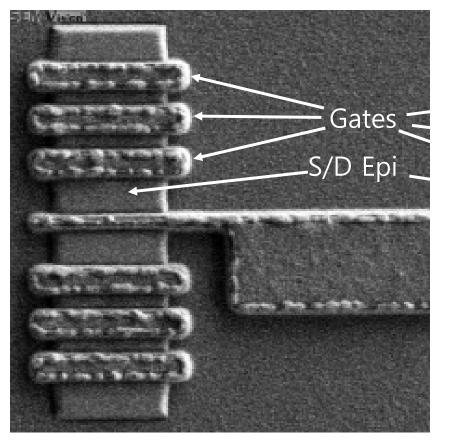

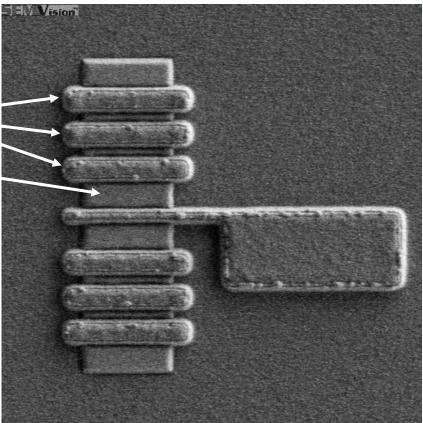

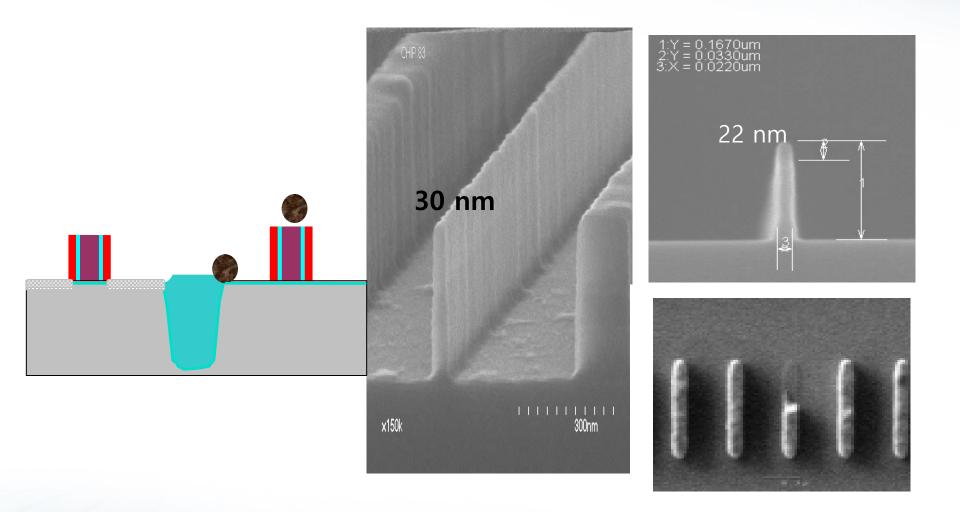

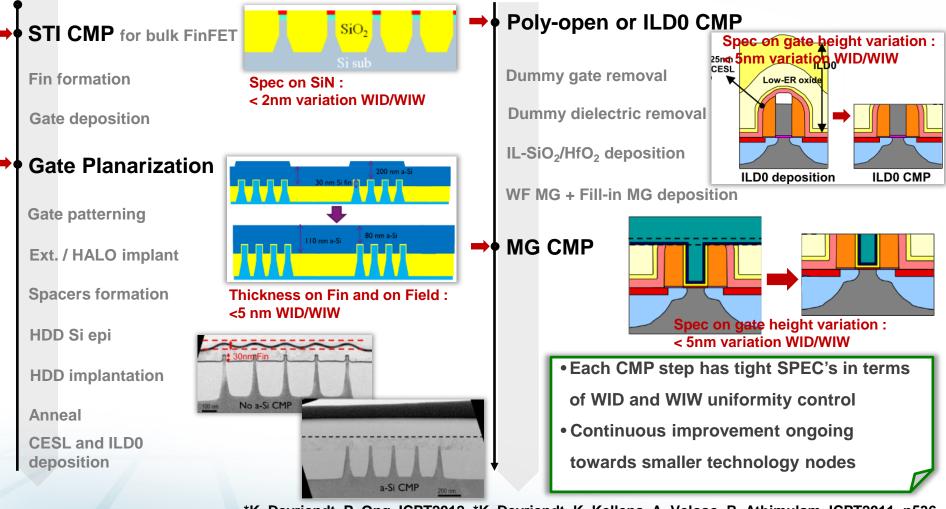

## **CMP Process for 3D FinFET -FEOL**

\* Critical CMP step in FEOP for sub-28 nm Replacement Metal Gate application (RMG)

#### FinFET technology have been described

\*K. Devriendt, P. Ong, ICPT2012, \*K. Devriendt, K. Kellens, A. Veloso, R. Athimulam, ICPT2011, p536

Nano-Bio Electronic Materials and Processing Lab.

#### How do we clean polished wafers?

(\*FOUP = Front Opening Unified Pod)

#### **CMP** Polishing Module FOUP\* FOUP\* Robot FOUP\* Transport Module Transport Module **Power Supply** Robot Unit 3<sup>rd</sup> Roll 1<sup>st</sup> Roll 2<sup>nd</sup> Roll Pen Brush < "E" CMP & P-CMP Tool > Brush Brush Brush & Spin Dry Cleaning Cleaning Cleaning CMP Polishing Module Megasoni Spray Je Dryer Robot Megasonic Spray Jet Dryer 2<sup>nd</sup> Roll 1<sup>st</sup> Roll Brush Brush 2000 Cleaning Cleaning

< "A" CMP & P-CMP Tool>

Cassette Line

#### **PVA Brushes!!**

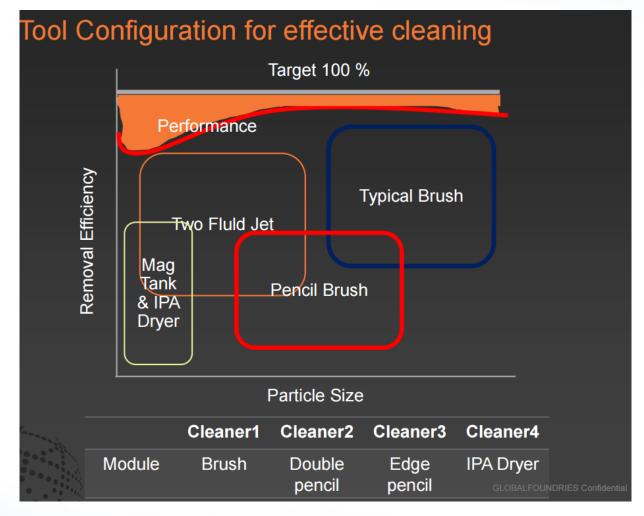

## Nano Particle Removal in Post CMP Cleaning

• Typical Brush (Large Particle) + Pencil Brush (Middle Particle)

GF, SPCC 2015

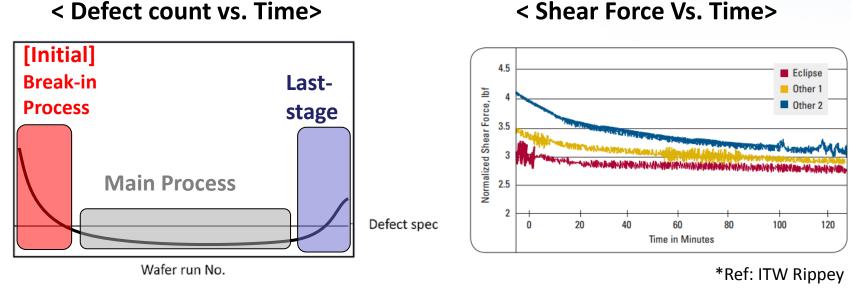

## **Defect Level of PVA Brush's Stage**

- Initial > Last-stage >> Main Process

- **Defect count is increased** by brush cleaning in long run process.

- Shear force is decreased by brush cleaning in long run process.

- PVA brush cleaning performance decreases as a function of process time.

Defect count

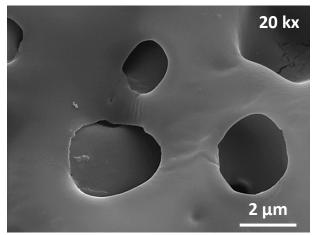

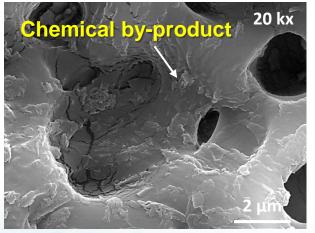

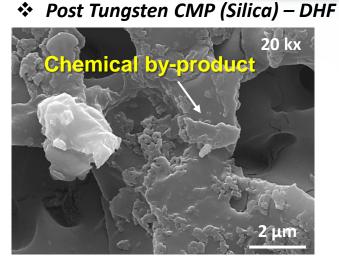

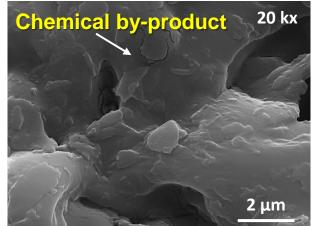

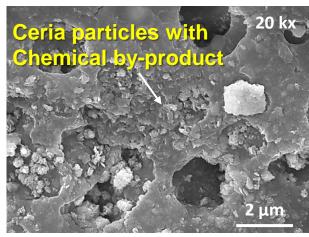

## **FE-SEM Analysis of Fully-Used PVA Brush**

#### New Brush

Post Oxide CMP (Silica)

SC-1 Cleaning

Post Oxide CMP (Silica)

DHF

Post Oxide CMP (Ceria)

DHF

• Different types of slurry and cleaning chemistry affect contamination of brush surface.

| # | Method               | Solution                                                                 | рН   |           |

|---|----------------------|--------------------------------------------------------------------------|------|-----------|

| 1 |                      | DIW                                                                      | 7    | Reference |

| 2 | Dipping<br>(24 Hr)   | DHF<br>(0.9:100 = HF:DIW)                                                | 3.1  | Condition |

| 3 | (2411)               | SC-1<br>(1:2:40 = NH <sub>4</sub> OH:H <sub>2</sub> O <sub>2</sub> :DIW) | 10.2 |           |

| 4 |                      | DIW                                                                      | 7    |           |

| 5 | Scrubbing<br>(12 Hr) | DHF<br>(0.9:100 = HF:DIW)                                                | 3.1  |           |

| 6 | (1211)               | SC-1<br>(1:2:40 = NH <sub>4</sub> OH:H <sub>2</sub> O <sub>2</sub> :DIW) | 10.2 |           |

- 2 Types of Method : Dipping / Scrubbing

- 3 Types of Solution : DIW / SC-1 / DHF

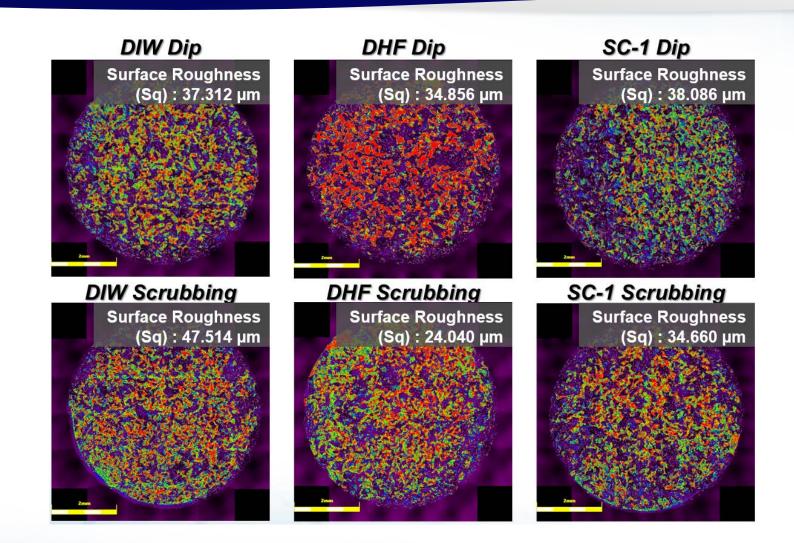

#### **3D-Profiler Analysis of Chemical Treated PVA Brushes**

- DHF scrubbed PVA brush shows flattened surface.

- SC-1 scrubbed PVA brush shows rough surface.

$$Sq = \sqrt{\iint_{a} (Z(x, y))^2 \, dx \, dy}$$

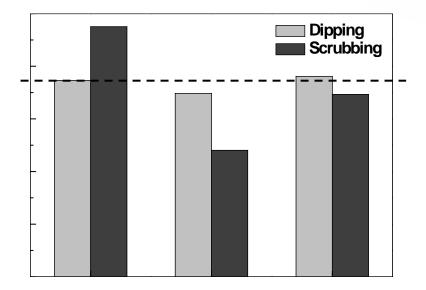

#### **3D-Profiler Analysis of Chemical Treated PVA Brushes**

#### Analyzed Surface Roughness of Various Chemical Treated PVA Brushes

- All dipped brushes show the similar morphology and surface roughness.

- The scrubbed brushes show significant change in morphology and surface roughness.

It will affect the change of real contact area between brush and particles on wafer.

- DHF scrubbed PVA brush shows flattened surface with the lowest surface roughness.

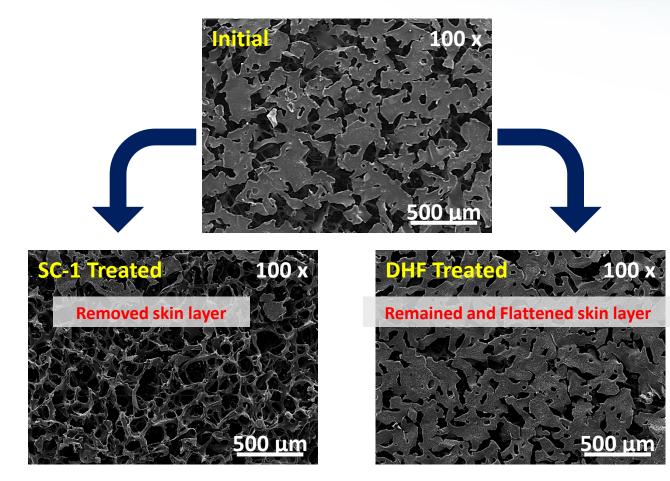

#### **FE-SEM Analysis of Chemical Treated PVA Brushes**

- SC-1 treated brush shows the removed skin layer.

- DHF treated brush shows remained and flattened skin layer.

It will affect the final cleaning performance on wafers.

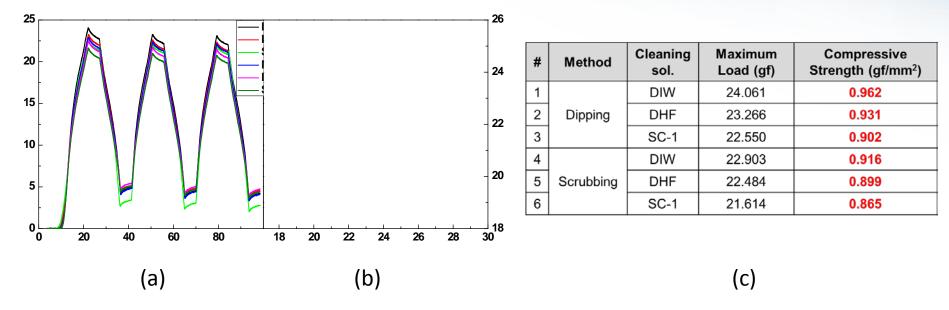

#### Compress Stress Analysis of Chemical Treated PVA Brushes

(a) compressive stress measurement of various chemical treated brushes, (b) its magnified region,(c) compressive strength

- A significant change of elastic property was observed in scrubbed brush when compared to the chemical dipped brush.

- The SC-1 treated brush showed more changes in its compressive stress than DHF treated brush.

#### **Effect of Brush Treatment Methods and Chemicals**

|                         | Dinning  | Scrubbing              |           |         |

|-------------------------|----------|------------------------|-----------|---------|

| Dipping                 |          | Overall                | DHF       | SC-1    |

| Surface morphology      | Similar  | Significant<br>changes | Flattened | Rough   |

| Surface roughness value | Similar  | Significant<br>changes | Lowest    |         |

| Skin layer              | Remained | Significant<br>changes | Remained  | Removed |

| Elastic property        | Similar  | Significant<br>changes |           | Lowest  |

- The scrubbed brushes show the significant changes in the morphology and surface roughness.

- The SC-1 treated brush shows more elastic and morphological changes than DHF treated brush.

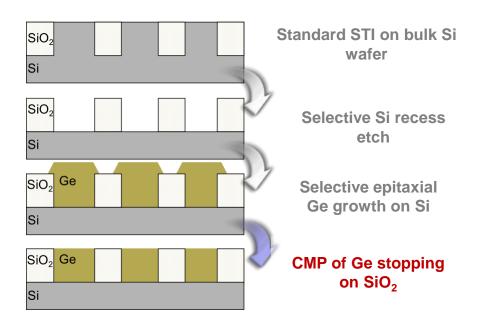

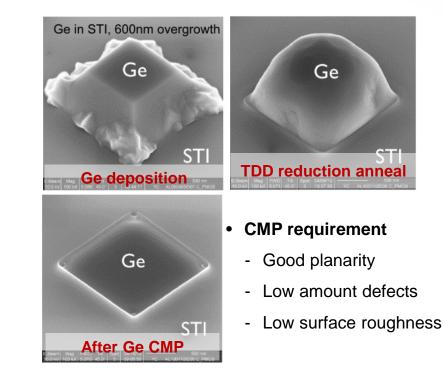

## CMP Process for High Mobility Channel Materials

#### \* CMOS performance can be enhanced by using high-mobility channel materials

- III/V materials (nMOS) : high electron mobility / Ge (pMOS) : high hole mobility

- The approach followed in this work is Ge-STI approach

\*P. Ong, C. Gillot, S. Ansar, B. Noller, Y. Li, L. Leunissen, ICPT2012, p23 \*P. Ong, L. Witters, ICPT2010, p69

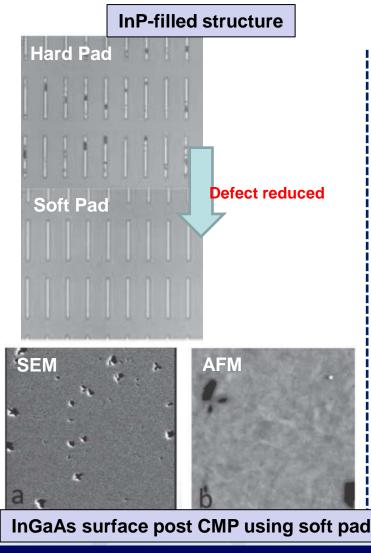

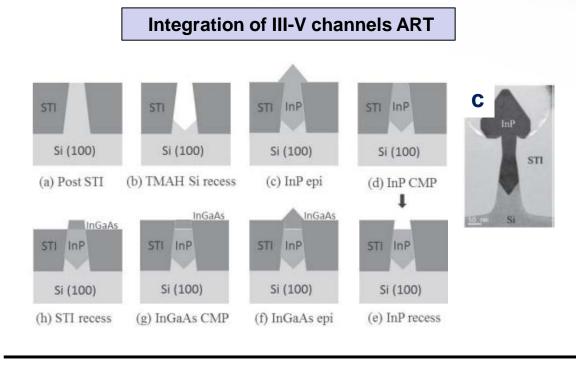

## Low Defectivity III-V CMP Process

#### Improving Defectivity for III-V CMP Processes for <10 nm Technology Nodes</p>

- InP in STI trenches can be removed by choosing the appropriate slurry/pad combination – Hard Pad < Soft Pad</li>

- Good surface achieved by using soft pad

- Not yet optimized on defect control on polished III-V surfaces

\*Lieve Teugels, Patrick Ong, Guillaume Boccardi, Niamh Waldron, ICPT2014, p15

Nano-Bio Electronic Materials and Processing Lab.

## HIG UNITERS

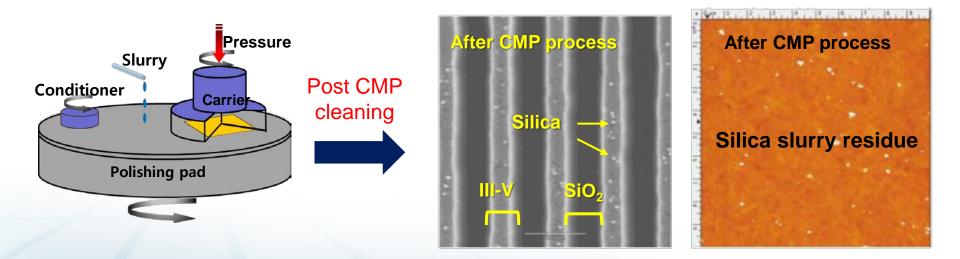

#### Issues of III-V post CMP cleaning

- InGaAs CMP using silica slurry

- Silica slurry abrasives were not removed perfectly after post CMP cleaning

- DIW megasonic followed by 2 brush steps with <1% diluted ammonia</li>

- Need to selective cleaning of III-V surface

- Chemical cleaning : etching, electro-repulsion

- ✓ Physical cleaning

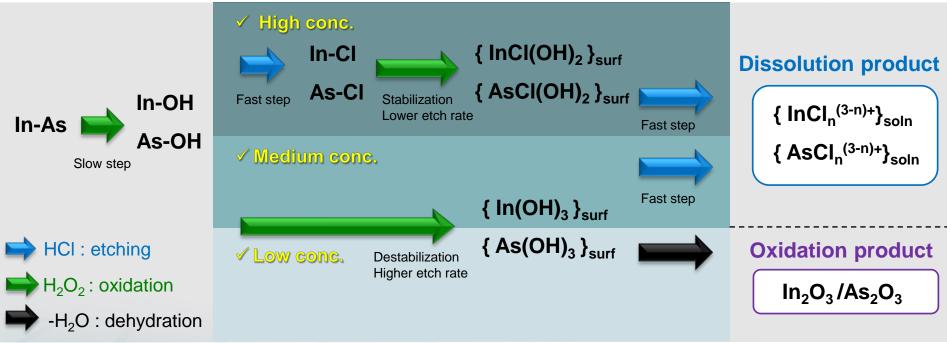

## InAs Etching Mechanism of SC-2

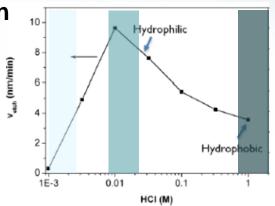

- Etching mechanism according to the HCI concentration

- ✓ High concentration: oxidation rate < dissolution rate</p>

- Low concentration : oxidation rate > dissolution rate

Dennis H. Van Dorp, Sophia Arnauts, Frank Holsteyns and Stefan De Gendt, ECS Journal of Solid State Science and Technology, 4(6) N5061-N5066 (2015)

Nano-Bio Electronic Materials and Processing Lab.

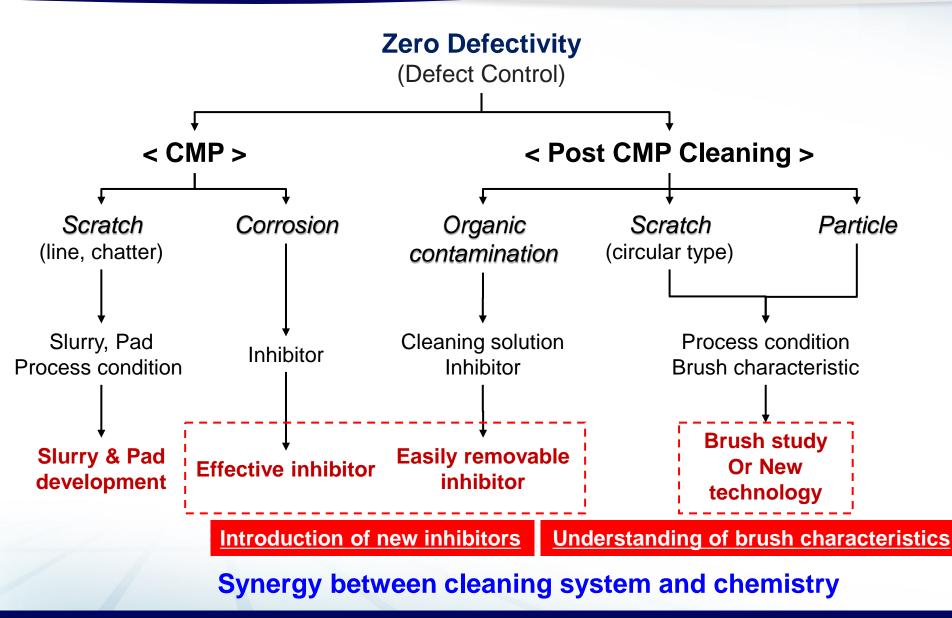

#### **Defect Control Map**

- CMP becomes more importance in 1x nm below device design and fabrication

- CMP Challenges : FEOL, MOL process- defect sensitive

- New consumable and cleaning technology needed

- Current cleaning process and technology are available and could solve all contamination issues in post CMP cleaning

#

Nano-Bio Electronic Materials and Processing Lab.